Innovate, Excel, Connect

Accton has an in-house developed FPGA/CPLD hardware architecture

Designed for server, data center switch, enterprise switch, and chassis systems. Each of the designs have a corresponding field-proven code base developed over years with ongoing continuous improvement.

Elevate Tech Connectivity

In the Dynamic Realm of FPGA/CPLD Development

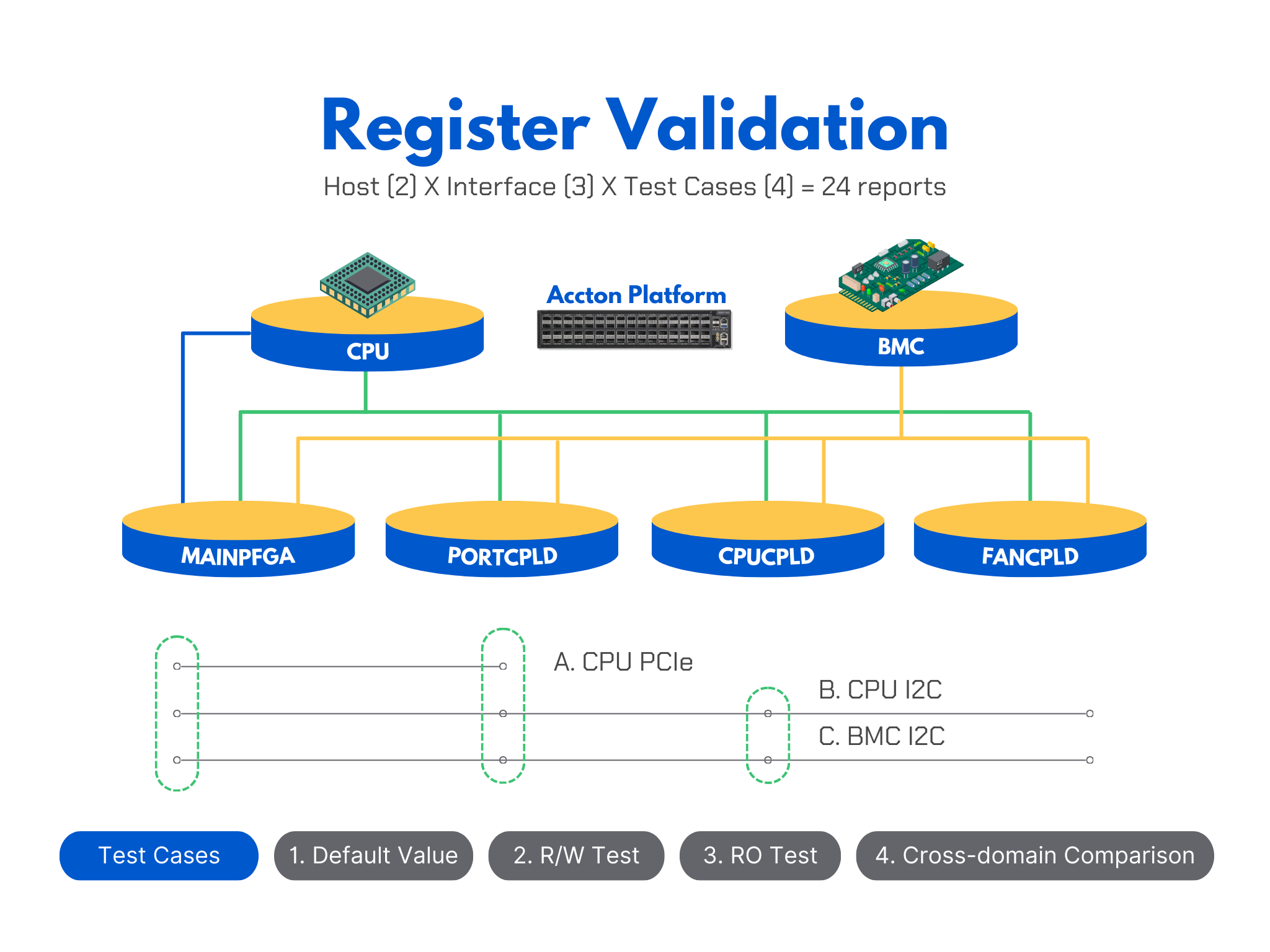

Register Validation

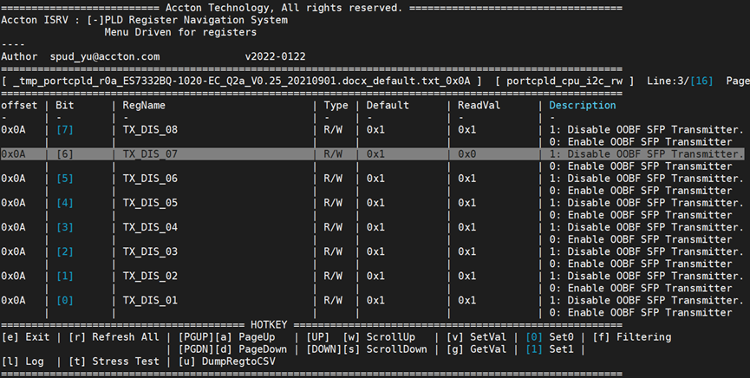

Accton has an in-house simulation framework called ISRV (in-system register validation) that does full register behavior validation, automatically comparing register behavior in the FPGA/CPLD specifications with the FPGA/CPLD image and generating reports. The ISRV also has an embedded menu-driven GUI in Accton DiagOS that can display all registers with their specification description.

Figure 1: Reports auto generation in ISRV

Figure 2: Menu-driven GUI with hotkey to validate registers in ISRV

Flexible Collaboration

Our design experience covers all FPGA/CPLD silicon vendors, and their most popular device families. From simple CPLD control logic to high-speed Ethernet, PCIe, and embedded processors, Accton offers customers flexible collaboration models.

Part Selection

From the earliest stage, Accton’s team works with customers on FPGA/CPLD part selection with utilization and power consumption analysis.

Whole-Chip Simulation

In the FPGA/CPLD RTL coding stage, we can help customers perform the whole chip simulation using Model-Simon and Questa-sim.

Synthesizable Shell Design

At the schematic design stage, in addition to meeting the FPGA/CPLD vendor’s checklist Accton also provides a synthesizable shell design for customers to make sure FPGA pin arrangement is correct.

Customer or Accton Specifications

Accton can follow a customers’ CSR and IP specification to develop an FPGA/CPLD project, or we can provide our own version for customer review.